Verifies that system clocks are within expected frequencies. More...

Macros | |

| #define | SL_IEC60730_TEST_CLOCK_MULTIPLIER 10 |

| Determines how many entrances into sl_iec60730_test_clock_tick() occur before bist frequency test executes. | |

| #define | SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ 10 |

| #define | SL_IEC60730_SYS_CLOCK_TEST_TOLERANCE 1 |

Enumerations | |

| enum | sl_iec60730_timer_test_control_t { SL_IEC60730_TIMER_TEST_DISABLE = 0, SL_IEC60730_TIMER_TEST_ENABLE = 1 } |

| Enable/disable switch for system timer test. More... | |

Functions | |

| void | sl_iec60730_sys_clock_count_tick (void) |

| void | sl_iec60730_test_clock_tick (void) |

| void | sl_iec60730_sys_clock_count_reset (void) |

| uint16_t | sl_iec60730_get_number_test_timer_tick (void) |

| void | sl_iec60730_sys_clock_test_enable (void) |

| void | sl_iec60730_sys_clock_test_disable (void) |

Detailed Description

Verifies that system clocks are within expected frequencies.

For IEC60730, a plausibility check must be performed to check that the system clock is running at a frequency with an expected bounds. This check requires that the system clock frequency be compared against a second, independent clock's frequency (test clock).

Hardware Architecture

EFR32 family devices provide a high frequency internal oscillator as well as a low frequency internal oscillator. The devices also provide timers modules that can be configured to use either oscillator as a clock source. These peripherals can be configured to vector code to interrupt service routines when the counter incremented by the peripheral and clocked by one of the clock sources meets certain criteria.

For timers, the criteria is a counter overflow event. The frequency of this overflow is defined by a reload value configured in firmware that hardware automatically loads into the timer's counter upon overflow.

Some timers offer a special mode where the timer's clock source is gated by a falling edge of the low frequency oscillator. In these cases, the system clock can be used as the clock source, and the number of timer counter ticks captured during the low frequency oscillator's logic low phase expresses the relationship between the two clocks.

The define SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ holds the ratio value between system clock timer interrupt period and test clock timer interrupt period, this value is used to compare with the system clock counter. The ratio value is divided by slow timer period (test clock timer interrupt period) and fast timer period (system clock timer interrupt period).

The tolerance of test (OEM set value of the define, config: SL_IEC60730_SYS_CLOCK_TEST_TOLERANCE) is typical (+/-) 10%-49% of the SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ.

Suggested OEM Configuration

Not every EFR32 device offers the same types of timers and clock sources. For this reason, the optimal resource usage on each device family varies. The following chart offers a suggested configuration for each EFR32 family. Firmware examples configure system and test timers as in Table 1

| EFR32 device | System timer | Test timer |

|---|---|---|

| Series 1 |

|

|

| Series 2 |

|

|

Failure Risks

The library's system clock plausibility test will force entry into safe state if the frequency relationship between the system clock and the test clock exceeds upper and lower bounds.

The library examines the relationship between the two clocks using calls that the OEM must place in OEM-defined timer interrupt service routines. Code examples for each EFR32 device provide drop-in firmware solutions for OEMs for timer initialization and ISR source code. OEMs must ensure that timer ISRs are able to be serviced promptly during operation.

Additionally, the OEM is responsible for leaving the system clock at a constant and defined operating frequency throughout all OEM firmware.

Finally, the OEM is responsible for setting sl_iec60730_timer_test_control to SL_IEC60730_TIMER_TEST_DISABLE within safety-critical code by calling function sl_iec60730_sys_clock_test_disable(). This value is only used in cases where the system is executing non-safety-critical code, where the BIST routine is also not being called. When returning to normal operation, clear all interrupt counters in iec60730 IRQ execution count, reset the timer clock tick and system clock tick timers, and set sl_iec60730_timer_test_control to SL_IEC60730_TIMER_TEST_ENABLE.

Software Architecture

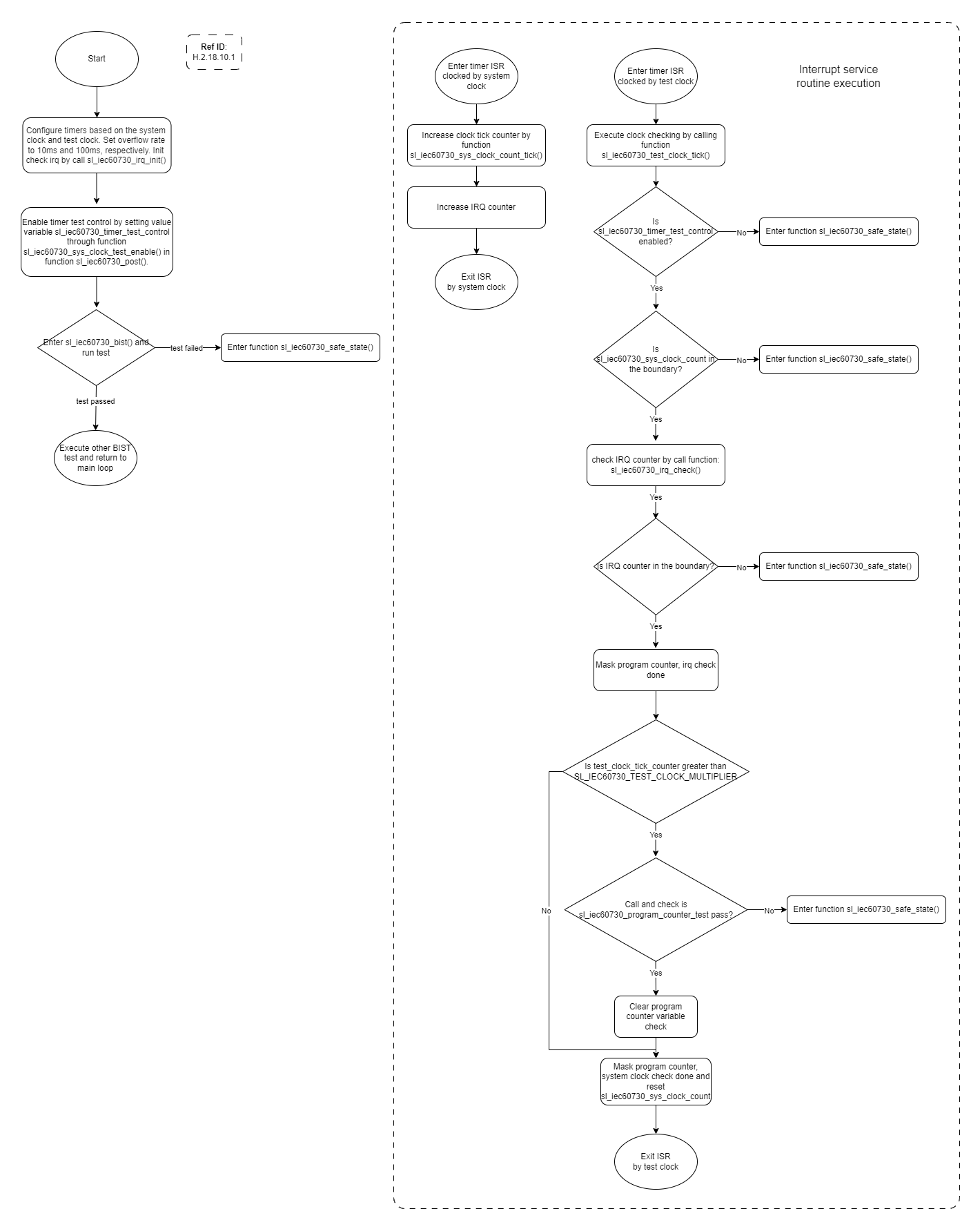

For the EFR32 IEC60730 implementation, Figure 1 shows the logic flow chart of the system clock frequency check during BIST. The test executes in the test timer interrupt, which runs as foreground calls to OEM functions and the foreground BIST test continuously execute.

Macro Definition Documentation

◆ SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ

| #define SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ 10 |

This define holds the ratio value between system clock timer interrupt period and test clock timer interrupt period

◆ SL_IEC60730_SYS_CLOCK_TEST_TOLERANCE

| #define SL_IEC60730_SYS_CLOCK_TEST_TOLERANCE 1 |

(OEM set value of the define) is typical (+/-) 10%-49% of the SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ.

Enumeration Type Documentation

◆ sl_iec60730_timer_test_control_t

Function Documentation

◆ sl_iec60730_get_number_test_timer_tick()

| uint16_t sl_iec60730_get_number_test_timer_tick | ( | void | ) |

public IEC60730 Get Timer Tick

- Returns

- sl_iec60730_number_test_timer_tick.

Function get value sl_iec60730_number_test_timer_tick, used for OEM testing

◆ sl_iec60730_sys_clock_count_reset()

| void sl_iec60730_sys_clock_count_reset | ( | void | ) |

public IEC60730 Initialize iec60730 timer tick variables

- Returns

- None.

This function should be called within the sl_iec60730_test_clock_tick() callback. During the initialization of the test clock timers, this function resets the internal test clock and system clock tick variables to known reset states.

◆ sl_iec60730_sys_clock_count_tick()

| void sl_iec60730_sys_clock_count_tick | ( | void | ) |

OEMs use the defines SL_IEC60730_SYS_CLOCK_TEST_CLK_FREQ and SL_IEC60730_SYS_CLOCK_TEST_TOLERANCE in the config file to define the expected tolerance and clock frequency of executions for each test clock tick included in a project. OEM code need to disable ISR-based timer test execution when in safe states. This local variable allows OEM code to test when events occur. static uint16_t sl_iec60730_number_test_timer_tick; Provides the expected ratio of system clock to test clock ticks Allows OEM code to run tests using timer tick. Must be defined as system clock (faster clock) / test clock (slower clock). The ratio value cannot exceed 0xFFFF.

This local variable allows customers to stop ISR-based tests when code enters a safe state where BIST is not being called because the code is not safety critical. Tests whose execution is gated by this value are the system clock test, the interrupt plausibility test, and the BIST execution frequency test. static uint8_t sl_iec60730_timer_test_control

This local variable allows customers to know the number of times the function sl_iec60730_test_clock_tick is called, used for customers testing static uint16_t sl_iec60730_number_test_timer_tick public IEC60730 System Clock Tick

- Returns

- None.

This function increments a system clock counter sl_iec60730_sys_clock_count, which is compared to a test clock counter as part of the system clock frequency check. It should be called in the timer interrupt service routine designated as the system clock timer in oem_iec60730_timer.c.

◆ sl_iec60730_sys_clock_test_disable()

| void sl_iec60730_sys_clock_test_disable | ( | void | ) |

public IEC60730 Disable Timer Test

- Returns

- None.

Function set sl_iec60730_timer_test_control to SL_IEC60730_TIMER_TEST_DISABLE.

◆ sl_iec60730_sys_clock_test_enable()

| void sl_iec60730_sys_clock_test_enable | ( | void | ) |

public IEC60730 Enable Timer Test

- Returns

- None.

Function set sl_iec60730_timer_test_control to SL_IEC60730_TIMER_TEST_ENABLE.

◆ sl_iec60730_test_clock_tick()

| void sl_iec60730_test_clock_tick | ( | void | ) |

public IEC60730 Test Clock Tick

- Returns

- None.

This function increments a test clock counter. The function executes all interrupt service routine-based IEC60730 tests, including the system clock frequency check. It should be called in the timer interrupt service routine designated as the test clock timer in oem_iec60730_timer.c.

1.8.17

1.8.17